Trace

Enverite Trace archiver augments the build flow with a tamper-evident audit trail

Trace

Enverite Trace archiver augments the build flow with a tamper-evident audit trail

Trace™ Archiver

FPGA Build Flow Traceability

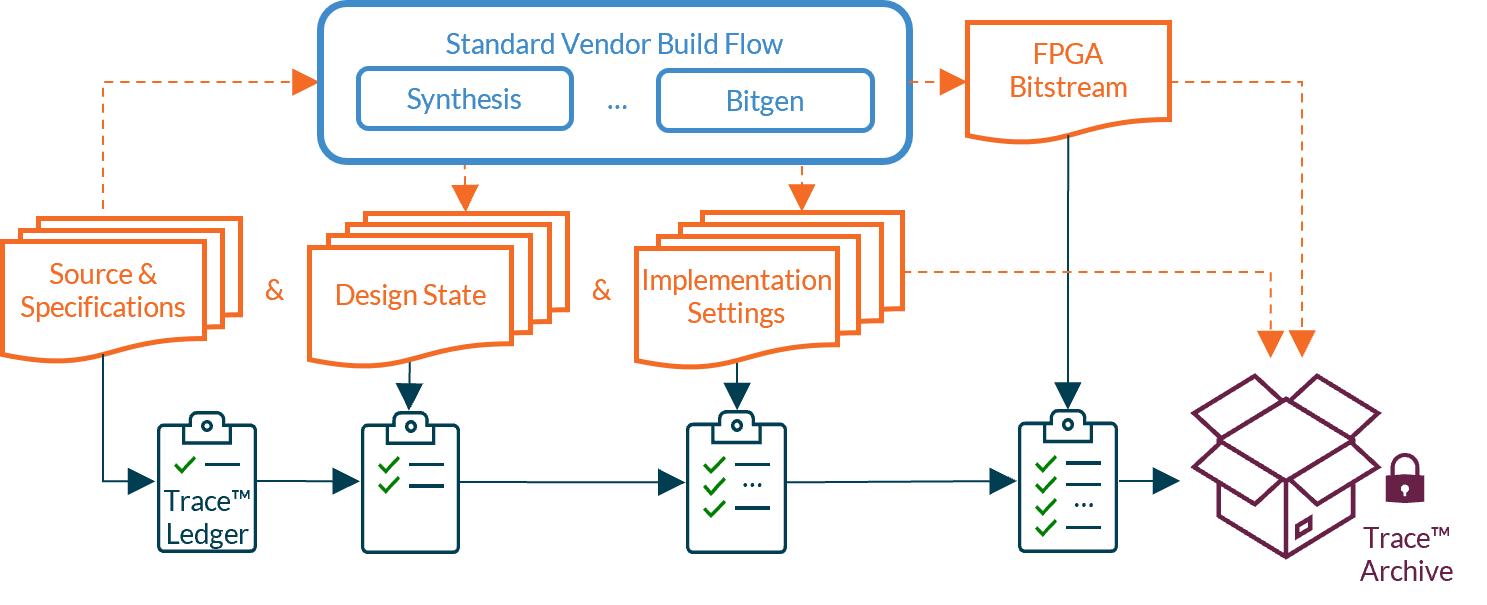

Enverite® Trace™ archiver creates and verifies a tamper-evident auditable digital thread as a design traverses the FPGA build flow. Trace™ archiver cryptographically signs design files, settings, and other artifacts, storing them in an archive to record the design process. Working alongside traditional vendor build flows, Trace™ archiver captures the design, extracts the relevant implementation artifacts before and after each implementation step, and applies cryptographic hashing and signature functions as integrity verification mechanisms. The implementation artifacts are preserved along with an electronic ledger containing the hash signatures in the Trace™ Archive.

EDA build flows are vulnerable

A sophisticated adversary can leverage Advanced Persistent Threats or Insider Threats to pick and choose where to insert vulnerabilities and malicious behaviors in FPGA and ASIC design implementations. They can target the design files (HDL source code), EDA software installations, IP libraries, intermediate design state, or the final deployed binary in the form of the configuration bitstream. Existing verification tools can verify functional equivalence or check properties at a given point in time, but the attacker is free to modify the design state or bitstream at any point after verification has been completed. With Trace™ archiver, we create a digital thread of the implementation flow that persists in time and can be audited with Retrace™ auditor at any point in the future.

Trace™ archiver augments your build flow with a tamper-evident audit trail

Trace™ archiver captures and preserves the design implementation state along with any design properties or implementation settings that would affect the build process as the design moves through the build flow. It does so without disturbing existing developer workflows or replacing EDA vendor tools by parsing the vendor project file (e.g., Vivado project.xpr) and generating a custom build script. This build script leverages vendor Tcl APIs to build the design, extract the relevant implementation artifacts before and after each implementation step, and apply cryptographic hashing and signature functions as integrity verification mechanisms. The implementation artifacts are preserved along with an electronic ledger containing the hash signatures in the Trace™ Archive.

Retrace

Enverite Retrace auditor enables audits and reproducible builds of the Trace archive

Retrace

Enverite Retrace auditor enables audits and reproducible builds of the Trace archive

Retrace™ auditor enables audits and reproducible builds

The Enverite® Retrace™ auditor authenticates the hash value signatures in the ledger and compares them to hash values recalculated from the files in the Trace™ Archive. It also enables manual inspection of implementation settings or an automated comparison to a provided list of required settings. If a design component were to be altered, a Retrace™ audit will detect the change and alert the user.

Retrace™ auditor also enables reproducible builds by automatically rebuilding the design using the source files and implementation settings (including seed values) stored in the Trace™ Archive and verifying equivalence between the original and rebuilt bitstreams. Reproducing builds on an independent IT system detects certain classes of indirect attacks that modify EDA software installations.

Trace™ archiver and Retrace™ auditor help you follow NSA guidance on FPGA assurance

The FPGA assurance guidelines released by NSA provide a list of mitigations against the introduction of Trojans during design development. One of these mitigations, Perform reproducible build, helps protect against an adversary that compromises the design cycle. The mitigation description is as follows:

A reproducible build process is a methodology to verify the integrity of the FPGA synthesis and build software. Reproducible build performs the synthesis process taking in human readable HDL, and other human readable inputs, and consistently generates the same final configuration file (bitstream)…This process will highlight the possession of modified software when there is a mismatch.

Trace™ archiver and Retrace™ auditor do exactly that! By cryptographically signing design artifacts and bundling them into a Trace™ Archive, the tools ensure that another user can confidently reproduce the design and detect any unexpected changes.

More Information

Use the Request Documents form to request the Trace™ whitepaper as well as other relevant documents.

If you’d like to contact us about using Trace™ archiver, or if you wish to see a product demonstration or have a product support question, contact us.